On their way to setting up a flexible and configurable 6G platform/ecosystem to enable fast integration of embedded intelligent systems and edge accelerators on advanced integrated circuit technologies, the VLSI team set up the digital flow and produced a first prototype of a neuromorphic SoC in the TSMC 65nm technology. The VLSI team, led by Dr. Martin Villemur and team members Daniel Klepatsch, Nicolas Rodriguez, Diego Gigena Ivanovich, and Messay Tamire-Tafeese was one of the main strategic milestones assigned to Dr. Pedro Julian as Head of the eAI Research Unit.

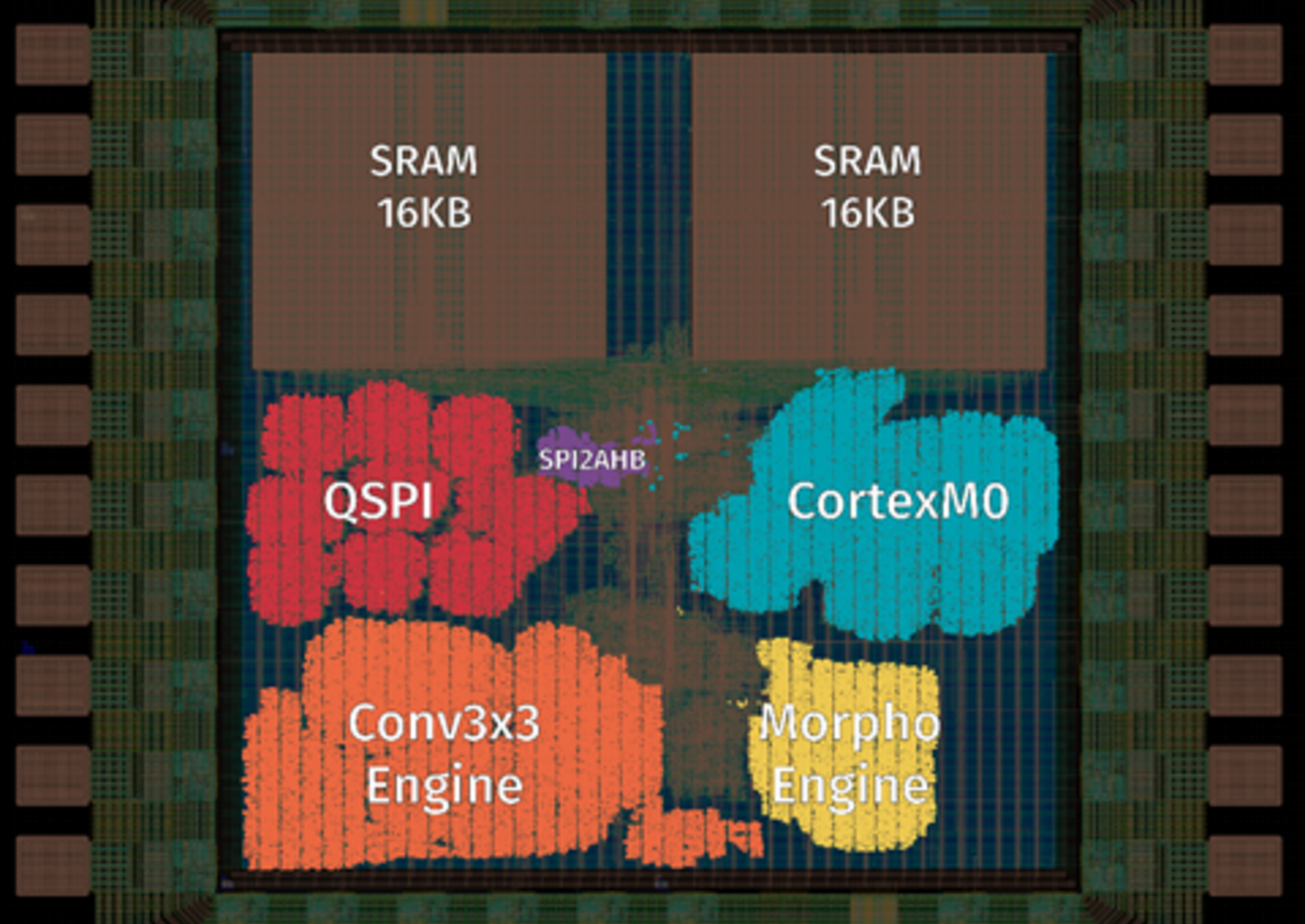

The system is composed of a processor with memory and communication infrastructure that interfaces two edge accelerators and an in-house IP block. The processor is an ARM Cortex M0 with a total of 32KB SRAM, SPI, UART, internal timers and an AMBA AHB bus --in order to make this possible, SAL joined the ARM Academic Access program. Connected to this bus, there is one in-house developed Quad SPI driver, a Morphological Neural Network custom accelerator designed by Nicolás Rodriguez as part of DIGINEURON (Simplicial computation) and a Convolutional Neural Network custom accelerator designed by Daniel Klepatsch as part of the FIRESAT project.