Auf dem Weg zum Aufbau einer flexiblen und konfigurierbaren 6G-Plattform/eines Ökosystems, das eine schnelle Integration von eingebetteten intelligenten Systemen und Randbeschleunigern auf fortschrittlichen integrierten Schaltkreistechnologien ermöglicht, hat das VLSI-Team den digitalen Fluss eingerichtet und einen ersten Prototyp eines neuromorphen SoC in der TSMC 65nm-Technologie hergestellt. Das VLSI-Team unter der Leitung von Dr. Martin Villemur und den Teammitgliedern Daniel Klepatsch, Nicolas Rodriguez, Diego Gigena Ivanovich und Messay Tamire-Tafeese war einer der wichtigsten strategischen Meilensteine, das mit Dr. Pedro Julian als Leiter der eAI-Forschungsabteilung durchgeführt wurde.

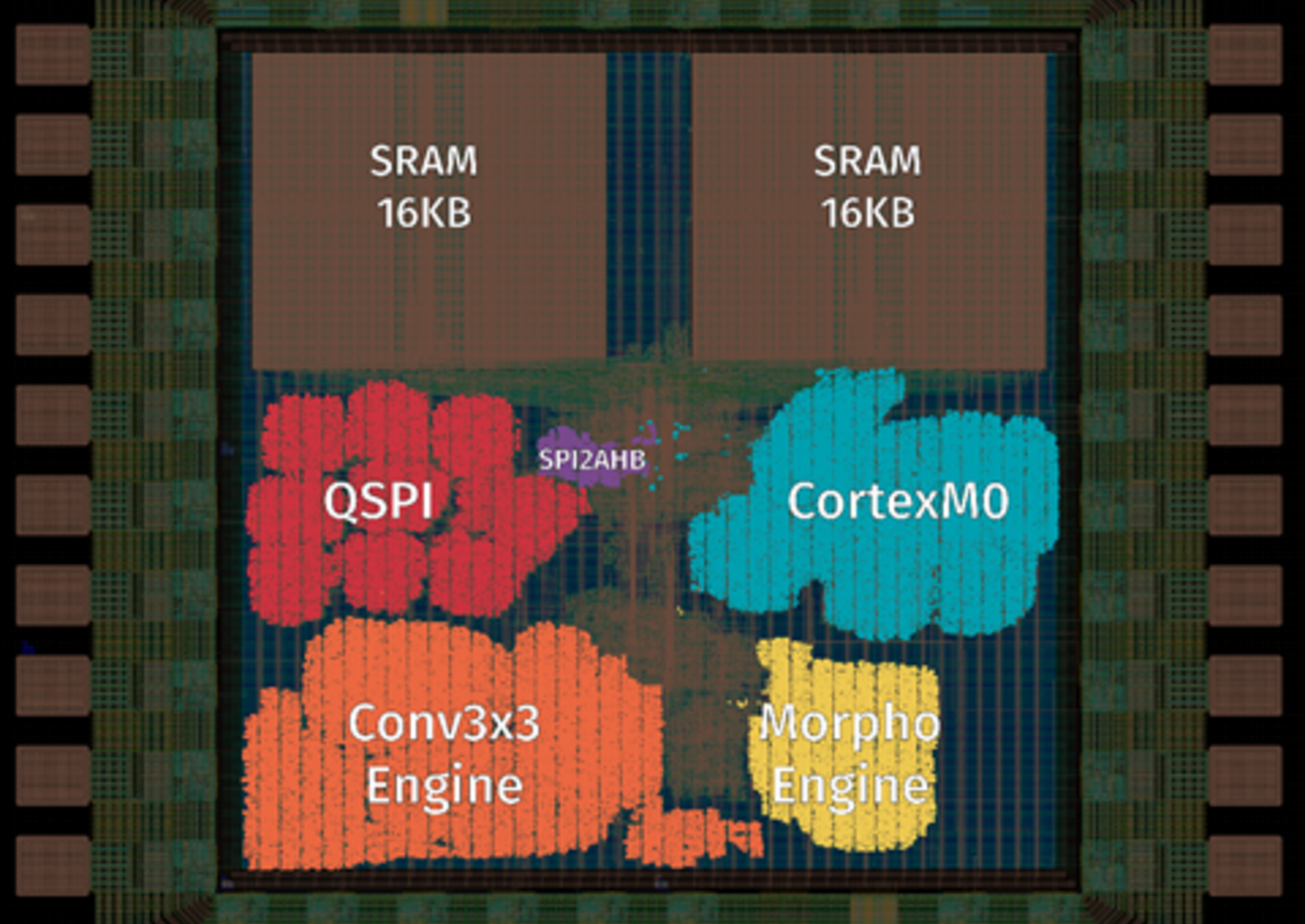

Das System besteht aus einem Prozessor mit Speicher und Kommunikationsinfrastruktur, der zwei Edge Accelerators und einen internen IP-Block verbindet. Der Prozessor ist ein ARM Cortex M0 mit insgesamt 32KB SRAM, SPI, UART, internen Timern und einem AMBA AHB-Bus - um dies zu ermöglichen, ist SAL dem ARM Academic Access Programm beigetreten. An diesen Bus angeschlossen sind ein intern entwickelter Quad-SPI-Treiber, ein von Nicolás Rodriguez im Rahmen von DIGINEURON (Simplicial computation) entwickelter kundenspezifischer Beschleuniger für ein Morphologisches Neuronales Netzwerk und ein von Daniel Klepatsch im Rahmen des FIRESAT-Projekts entwickelter kundenspezifischer Beschleuniger für ein Convolutional Neural Network.

Der Kern des Chips hat eine Fläche von 0,55 mm2 und wird voraussichtlich mit einer Frequenz von mindestens 100 MHz arbeiten.